# TECHNOLOGIES

Material and Design Advances in Silicon-on-Insulator Substrates to Improve Nuclear Physics Sensors and Circuits

August 13, 2024

Redacted Copy for Distribution

Caporus Technologies, Inc

## Intro to Caporus & NLP™

### Silicon on Insulator for NP

### Intro to Caporus & NLP™

## Silicon on Insulator for NP

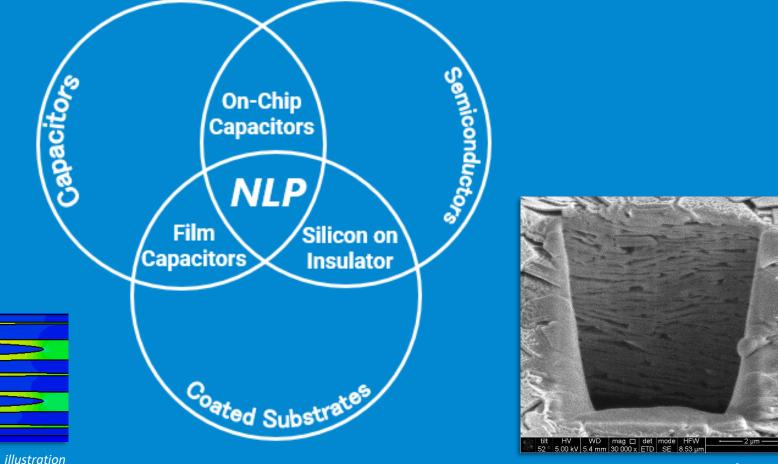

#### Caporus NLP<sup>TM</sup>

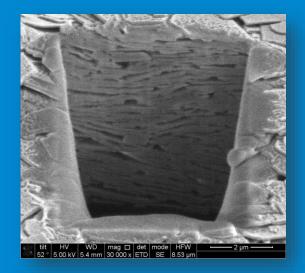

**Nanoscale Lamellar Porosity**<sup>™</sup> (NLP<sup>™</sup>)

Controls the electric field distribution within a porous ceramic structure

FIB image of material

Caporus Technologies, Inc.

10 µm

### **NLP™ Technology** | **Production at Scale**

>10 L Slurry Production

Compatible with High-Volume Roll-to-Roll Manufacturing Demonstrated Nanoscale Lamellar Porosity over Large Areas

*Slurry-based coating for R2R deposition of ceramic coating - No sintering required*

#### NLP | Issued IP

FIG. 9

C 900

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | (19) 国家知识产校                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 又局<br>(12)发明专利<br>JP 7026850 B2 2022.2.28                                                                            | <ul> <li>(10) 授权公告号 CN 113168932 B</li> <li>(45) 授权公告日 2022. 06. 07</li> <li>(乳文・安徳舎・奥康纳</li> </ul>                                                                                                                                                                                           | USPTO<br>JPO | issued July 2020<br>issued March 2022             |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|---------------------------------------------------|

| (12) United States Patent<br>O'Connor<br>(45) Date of D                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Patent: Jul. 28, 2020                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | (11)特許番号<br><b>特許第7026850号</b><br>( <b>P7026850</b> )<br>)登録日 令和4年2月17日(2022.2.17)<br>Z<br>1 P<br>X 22 (全37頁) 最終頁に続く | <ul> <li>建机构 深圳中一联合知识产权代理<br/>有限公司 44414</li> <li>注理师 王丽</li> <li>1.</li> <li>3/16 (2006.01)</li> <li>3/56 (2006.01)</li> <li>17/36 (2006.01)</li> <li>17/36 (2006.01)</li> <li>2件</li> <li>11017494 A1,2011.01.27</li> <li>D8185728 A1,2008.08.07</li> <li>D4195693 A1,2004.10.07</li> </ul> | EPO          | issued June 2022<br>pending<br>filings in process |

| ELECTRICAL INSULATION WITH VACUUM<br>OR GAS       U.S. P.         (71) Applicant: Kevin Andrew O'Connor, Orland<br>Park, IL (US)       9,870,875 B1*<br>2004/0195693 A1<br>2004/0195782 A1<br>2011/0017494 A1         (72) Inventor: Kevin Andrew O'Connor, Orland<br>Park, IL (US)       0TH         (*) Notice: Subject to any disclaimer, the term of this<br>patent is extended or adjusted under 35<br>U.S.C. 154(b) by 0 days.       International Search Re<br>151974 dated Dec. 18,<br>* cited by examiner         (21) Appl. No.: 16/576,438       Primary Examiner<br>(74) Attorney, Agent<br>US 2020/0090866 A1 Mar. 19, 2020       (57) | 10/2004 Kloster et al.<br>8/2008 Clevenger et al.<br>1/2011 Asokan et al.<br>ER PUBLICATIONS<br>port and Written Opinion for PCT/US19/<br>2019.<br>Eric W Thomas<br>or Firm — Husch Blackwell LLP<br>ABSTRACT                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                      | 70875 B1,2018.01.16<br>96589 A,2007.07.11<br>4 刘平<br>建业书2页 说明书22页 附图29页                                                                                                                                                                                                                       |              |                                                   |

| <ul> <li>(60) Provisional application No. 62/733,174, filed on Sep. 19, 2018.</li> <li>(51) Int. CL <ul> <li>(60) Provisional application No. 62/733,174, filed on Sep. 19, 2018.</li> <li>(51) Int. CL</li> <li>(51) Int. CL</li> <li>(61) HOIG 4/20 (2006.01)</li> <li>(70) HOIG 4/20 (2006.01)</li> <li>(71) HOIG 4/20 (2006.01)</li> <li>(72) U.S. CL</li> <li>(72) CP</li></ul></li></ul>                                                                                                                                                                                                                                                      | e including solid dielectric regions<br>diity of regions of vacuum or gas is<br>tric constant of the regions of solid<br>dielectric constant greater than 4. Each<br>gions of vacuum or gas or the regions<br>ay be anisotropic with an aspect ratio<br>nallest average dimension of a plurality<br>or gas and/or solid dielectrics can have<br>I micron. The dielectric structure may<br>ical energy density in the regions of<br>i in the solid matrix. One or more<br>active structure can be coated with a<br>without an interface between a region<br>d electrode. ms, 29 Drawing Sheets | )1 つ又は複数の領域であって<br>うちの少なくとも 1 つの領域は<br>ξ (d m i n )を有する、 1 つ                                                         |                                                                                                                                                                                                                                                                                               | 902          | 904                                               |

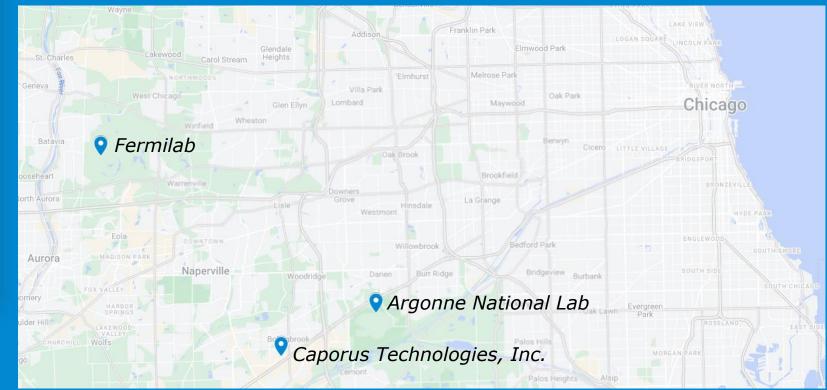

#### *Caporus is located near Fermilab and Argonne in Southwest Chicagoland*

*Caporus was previously embedded at Argonne through the Chain Reaction Innovations program*

CHAIN REACTION

Entrepreneurship at Argonne

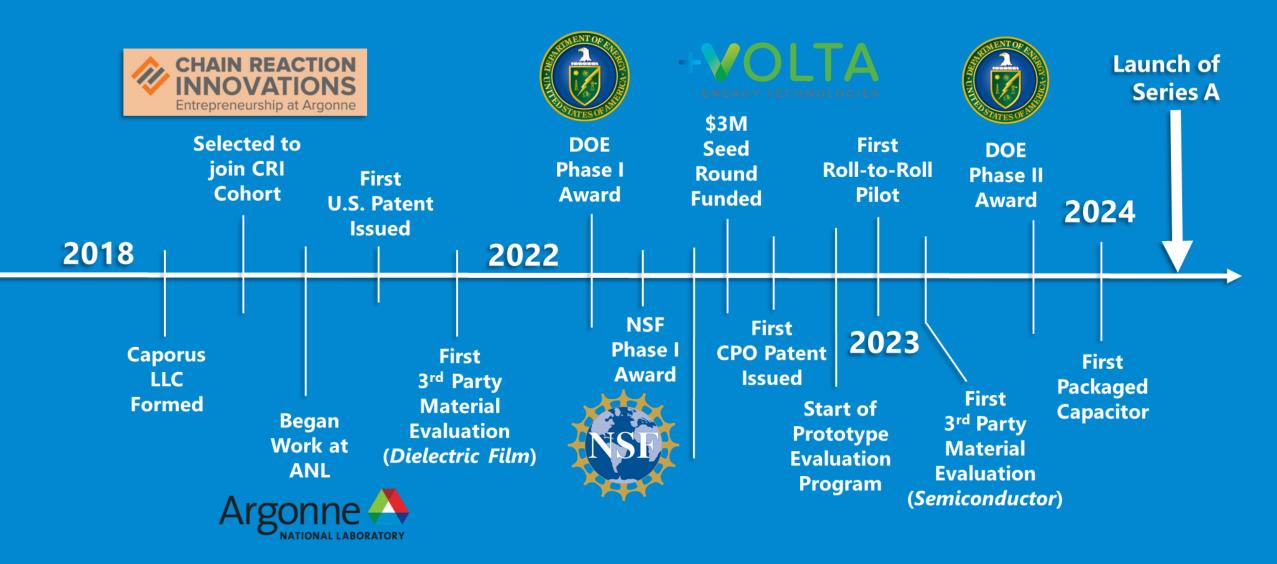

#### **Timeline and Milestones**

#### Caporus | Team

# TECHNOLOGIES

#### **BOARD OF DIRECTORS**

Kevin O'Connor, PhD Founder and CEO

David Schroeder Chief Technology Officer Volta Energy Technologies

Jim Cable Former CEO Peregrine Semiconductor

Caporus Technologies, Inc

# Intro to Caporus & NLP™

### Silicon on Insulator for NP

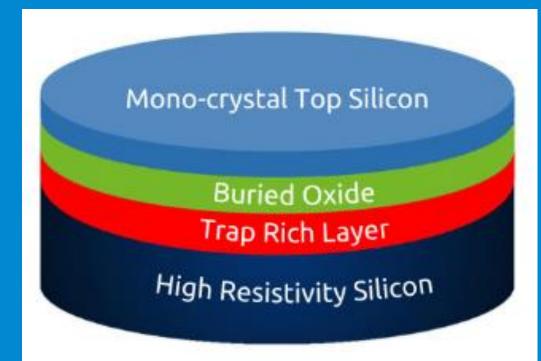

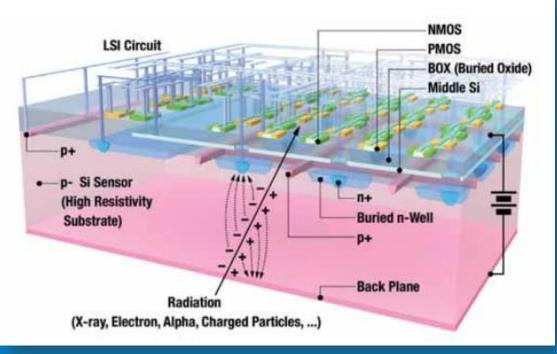

### Silicon on Insulator (SOI)

Commercial RF-SOI Substrate Structure

Image from SOITEC

| SOI Advantages         | SOI Disadvantages                                  |  |  |

|------------------------|----------------------------------------------------|--|--|

| Superior Single Event  | Total Ionizing Dose Issues                         |  |  |

| Upset Tolerance        | (Charge Effects)                                   |  |  |

| Better Noise Isolation | Radiation Damage to BOX                            |  |  |

| Speed                  | Back-gate Effect due to Field<br>Applied in Sensor |  |  |

| Density                | Coupling of Charges in BOX<br>and sensor           |  |  |

#### **Improved SOI for MAPS**

- Reduce unwanted coupling between substrate and front-end electronics

- Reduced back-gate effect

- Improve sensitivity

- Reduce noise

- Improved radiation hardness

- Lower radiation cross-section

- Reduced coupling decreases effects of trapped charges

- Elimination of inversion layer effects

- Enable depletion with applied electric field

- Improve sensitivity

SOIPIX – 2016 KEK Annual Report

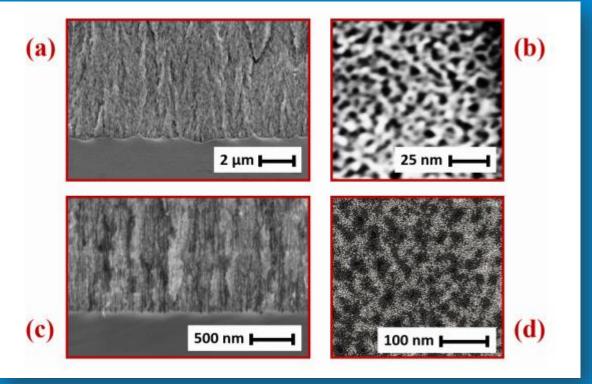

### NLP | Porous Si SOI

- Porous Si SOI

- State-of-the-art in research

- Porous Si layer between silica and silicon

- Electrochemical etching of Si

- Columnar porosity

- Advantages

- Trap-rich and low dielectric constant

- Record-high linearity (RF)

- Reduced substrate noise, coupling and parasitics

- Disadvantages

- Poor mechanical stability (>50% porosity)

- Sometimes requires doped substrates to increase conductivity for electrochemical etching (\$)

M. Rack, UCL Dissertation, 2021

### NLP Porous Si SOI

- Advantages over Standard Si

- High effective resistivity due to trap layers at pore interfaces

- Advantages over Trap-Rich SOI

- Potential for record-high linearity

- Reduced substrate noise coupling levels and associated parasitics

- Advantages over Porous Si

- Equal or potentially lower effective permittivity

- Lower porosity required for given effective permittivity higher mechanical strength due to higher solid content

- Higher mechanical strength due to pore structure highly resistant to crushing/breaking from compaction

- Compatible with any substrate resistivity (e.g. compatible with HR or std Si) – no need for low resistivity for electrochemical porosification

- No need for post-processing to implement porosity (e.g. no etch-stop layers, patterning, etc.)

## Intro to Caporus & NLP<sup>TM</sup>

### Silicon on Insulator for NP

### Phase II Project Summary

- Priorities from Solicitation

- Next generation of monolithic active pixel sensors (MAPS)

- Radiation hardness (EIC luminosity of  $10^{33} 10^{34}$  cm<sup>-2</sup>s<sup>-1</sup>)

- Apply E-field to substrate to fully deplete detection volume

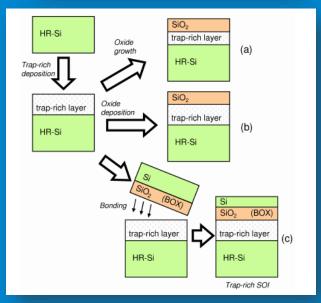

- Proposed Technology

- Implement MAPS on SOI

- Improved single-event upset, better noise isolation, speed, and density compared to bulk process

- Modified SOI with porous Si below BOX

- Reduce capacitive coupling between Si layers (Lower  $\varepsilon_{eff}$  and greater non-BOX thickness of porous Si)

- Reduce radiation cross-section of BOX and total ionizing dose effects

- Eliminate parasitic conduction layer at interface of BOX and bulk Si (Trap-rich)

- Phase II Demonstration

- 1. Scale processes for radiation testing

- 2. Etching processes for porous layer

- 3. Design CMOS and test structures

- 4. Fabricate test devices

- 5. Test for radiation hardness

- With and without porous layer

- As-received and after irradiation

#### **Phase II Resources**

#### **Phase II Team**

- Caporus Technologies

- Kevin O'Connor (PI)

- Nikki Chang

- Karabi Mondal

- Eric Acosta

- Bill Fortino

- Michael Boehme

- Jim Cable (Consultant SOI Development and Commercialization)

- Francis Chapman (Consultant Materials Development)

- Subaward

- Fermi National Accelerator Laboratory

- Farah Fahim, Davide Braga, and Xiaoran Wang (SOI – MAPS Design, Irradiation, Device Testing)

#### **Additional Resources**

- SkyWater (Vendor)

- Device fabrication

- Foley and Lardner (TABA)

- IP: USPTO and PCT applications

- Contracts: Commercial engagement pilot and license

- External Facilities

- Center for Nanoscale Materials (CNM)

- Liliana Stan and Ralu Divan (SciCon)

- UChicago Pritzker Nanofabrication Facility

- Northwestern NUFAB

- Carl Traynor (Consultant Commercialization)

Caporus Technologies, Inc.

#### Asks from NP Community

- Addressing Vendor Schedule Risk

- Availability of SkyWater RH90 process is delayed

- Investigating alternatives for fabrication of test structures

- CMOS processing on SOI substrates preferred

- Connections within DOE Community

- End users of MAPS detectors

- Detector development community

#### <u>Contact</u> PI: Kevin O'Connor oconnorka@caporus.com